Classe de terminale NSI Le contrôle de redondance cyclique La somme de contrôle

Publié le 19/03/2021

Extrait du document

«

Classe de terminale NSI

Le contrôle de redondance cyclique

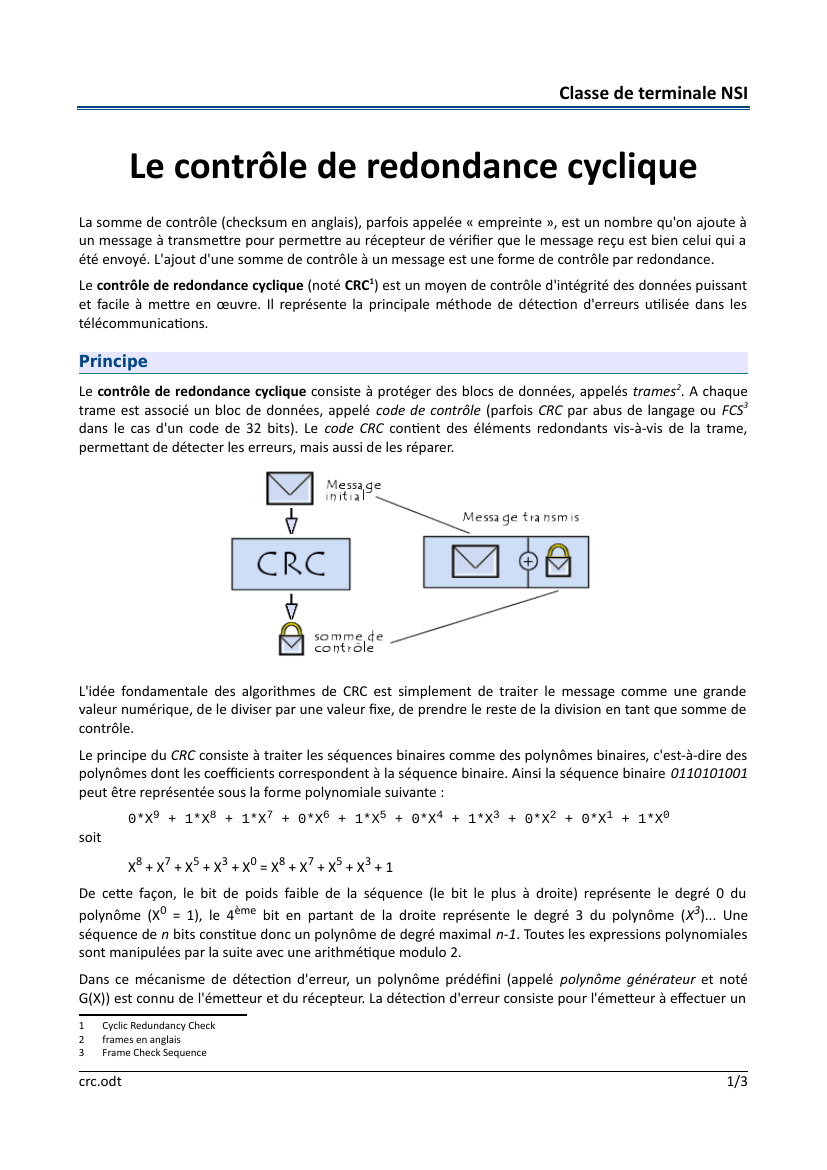

La somme de contrôle (checksum en anglais), parfois appelée « empreinte », est un nombre qu'on ajoute à

un message à transmettre pour permettre au récepteur de vérifier que le message reçu est bien celui qui a

été envoyé.

L'ajout d'une somme de contrôle à un message est une forme de contrôle par redondance.

Le contrôle de redondance cyclique (noté CRC 1

) est un moyen de contrôle d'intégrité des données puissant

et facile à mettre en œuvre.

Il représente la principale méthode de détection d'erreurs utilisée dans les

télécommunications.

Principe

Le contrôle de redondance cyclique consiste à protéger des blocs de données, appelés trames 2

.

A chaque

trame est associé un bloc de données, appelé code de contrôle (parfois CRC par abus de langage ou FCS 3

dans le cas d'un code de 32 bits).

Le code CRC contient des éléments redondants vis-à-vis de la trame,

permettant de détecter les erreurs, mais aussi de les réparer.

L'idée fondamentale des algorithmes de CRC est simplement de traiter le message comme une grande

valeur numérique, de le diviser par une valeur fixe, de prendre le reste de la division en tant que somme de

contrôle.

Le principe du CRC consiste à traiter les séquences binaires comme des polynômes binaires, c'est-à-dire des

polynômes dont les coefficients correspondent à la séquence binaire.

Ainsi la séquence binaire 0110101001

peut être représentée sous la forme polynomiale suivante :

0*X 9

+ 1*X 8

+ 1*X 7

+ 0*X 6

+ 1*X 5

+ 0*X 4

+ 1*X 3

+ 0*X 2

+ 0*X 1

+ 1*X 0

soit

X 8

+ X 7

+ X 5

+ X 3

+ X 0

= X 8

+ X 7

+ X 5

+ X 3

+ 1

De cette façon, le bit de poids faible de la séquence (le bit le plus à droite) représente le degré 0 du

polynôme (X 0

= 1), le 4 ème

bit en partant de la droite représente le degré 3 du polynôme ( X 3

)...

Une

séquence de n bits constitue donc un polynôme de degré maximal n-1 .

Toutes les expressions polynomiales

sont manipulées par la suite avec une arithmétique modulo 2.

Dans ce mécanisme de détection d'erreur, un polynôme prédéfini (appelé polynôme générateur et noté

G(X)) est connu de l'émetteur et du récepteur.

La détection d'erreur consiste pour l'émetteur à effectuer un

1 Cyclic Redundancy Check

2 frames en anglais

3 Frame Check Sequence

crc.odt 1 / 3.

»

↓↓↓ APERÇU DU DOCUMENT ↓↓↓

Liens utiles

- Corrigé contrôle matrice Terminale

- DM d’Histoire Contrôle n°1 sur la guerre froide (Terminale)

- Introduction au droit européen classe de terminale

- Classe de Terminale correction du DS n°1: Crise économique de 1929

- Grand Oral : récursivité et récurrence (maths/ NSI)